Timing-Diagramm

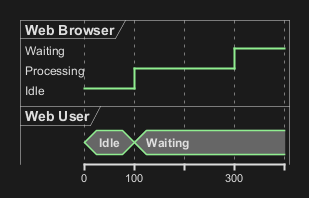

Ein Timing-Diagramm in der UML ist eine spezielle Art von Interaktionsdiagramm, das die zeitlichen Beschränkungen eines Systems visualisiert. Es konzentriert sich auf die chronologische Reihenfolge von Ereignissen und zeigt, wie verschiedene Objekte im Laufe der Zeit miteinander interagieren. Zeitdiagramme sind besonders in Echtzeitsystemen und eingebetteten Systemen nützlich, um das Verhalten von Objekten über einen bestimmten Zeitraum hinweg zu verstehen. [Ref. of initial request QA-5383] Definition von Elementen und Teilnehmern

Definition von Elementen und Teilnehmern

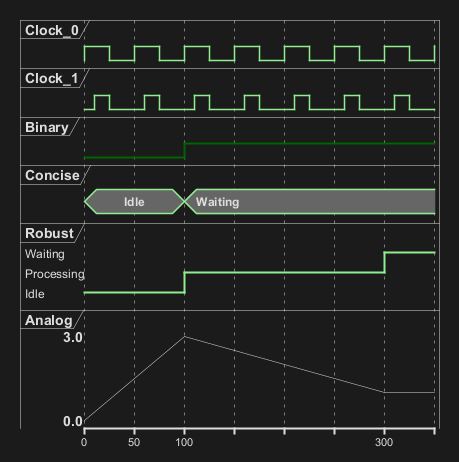

Schlüsselwörter steuern die Darstellung der Teilnehmer in der Grafik. Mit folgenden Schlüsselwörtern kann die Darstellung gesteuert werden:

| Schlüsselwort | Beschreibung |

analog

|

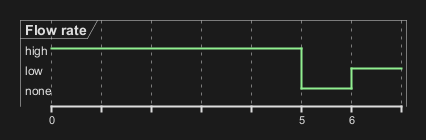

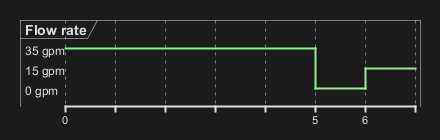

analog stellt den Statusübergang des Teilnehmers als analoges Signal dar, in dem die angegebenen Werte der Stati linear über die in der Zeitlinie gesetzten Zeitpunkte interpoliert werden.

|

binary

|

binary Lässt für den Teilnehmer zwei Status zu, zwischen denen er wechseln kann

|

clock

|

clocked stellt eine Rechtecksignal für den Teilnehmer dar.Mit period wird die Frequenz für den Statuswechsel festgelegt (Muss-Angabe).Mit offset kann der Startzeitpunkt des ersten Signals festgelegt werden.Mit pulse kann die länge des Statusimpulses festgelegt werden

|

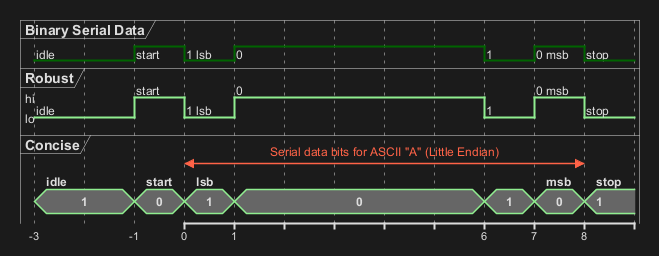

concise

|

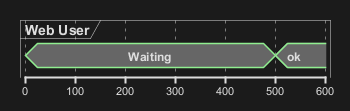

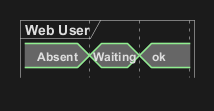

concise ist eine vereinfachte Darstellung um einen Statusübergang eines Teilnehmers darzustellen (Eignet sich am besten für die Darstellung von Meldungssignalen).

|

robust

|

robust stellt eine Signallinie dar, welche den Übergang von verschiedenen Statusübergängen darstellt.

|

@ festgelegt.

Der jeweilige Status des Teilnehmers zu diesem Zeitpunkt wird mit is definiert.

|

🎉 Copied!

|

|

|

🎉 Copied!

|

|

[Ref. QA-14631, QA-14647 and QA-11288] [Ref. QA-14631, QA-14647, QA-11288 and GH-2409]

WARNING

This translation need to be updated. WARNING

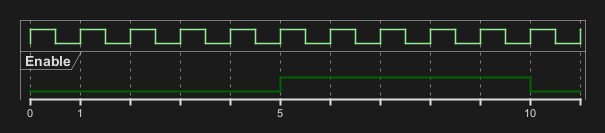

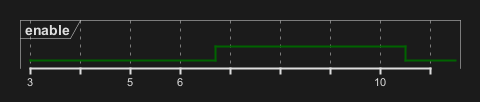

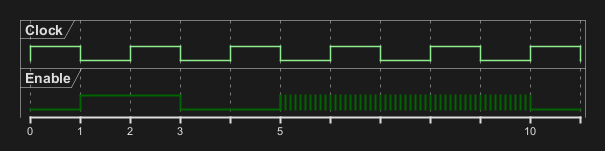

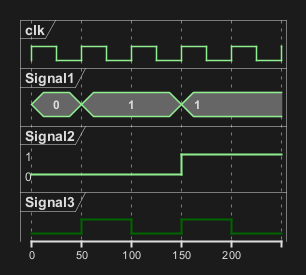

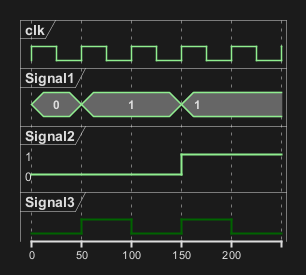

Binary and Clock

Binary and Clock

It's also possible to have binary and clock signal, using the following keywords:

binaryclock

|

🎉 Copied!

|

|

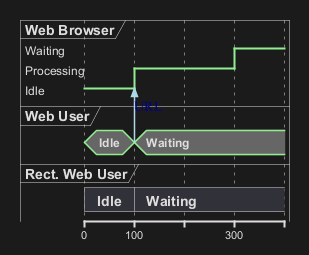

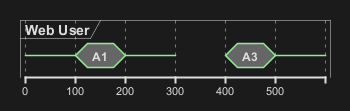

Adding message

Adding message

You can add message using the following syntax.

|

🎉 Copied!

|

|

Relative time

Relative time

It is possible to use relative time with @.

|

🎉 Copied!

|

|

Anchor Points

Anchor Points

Instead of using absolute or relative time on an absolute time you can define a time as an anchor point by using the as keyword and starting the name with a :.

@XX as :<anchor point name>

|

🎉 Copied!

|

|

Anchor Points with decimal offset

Anchor Points with decimal offset

|

🎉 Copied!

|

|

[Ref. QA-17885]

Participant oriented

Participant oriented

Rather than declare the diagram in chronological order, you can define it by participant.

|

🎉 Copied!

|

|

Setting scale

Setting scale

You can also set a specific scale.

|

🎉 Copied!

|

|

When using absolute Times/Dates, 1 "tick" is equivalent to 1 second.

|

🎉 Copied!

|

|

Initial state

Initial state

You can also define an inital state.

|

🎉 Copied!

|

|

Intricated state

Intricated state

A signal could be in some undefined state.

Intricated or undefined robust state

|

🎉 Copied!

|

|

Intricated or undefined binary state

|

🎉 Copied!

|

|

[Ref. QA-11936 and QA-15933]

Hidden state

Hidden state

It is also possible to hide some state.

|

🎉 Copied!

|

|

|

🎉 Copied!

|

|

[Ref. QA-12222]

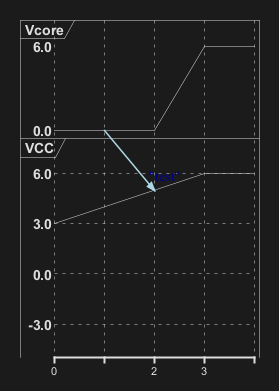

Negative time value

Negative time value

|

🎉 Copied!

|

|

[Ref. QA-7698]

Hide time axis

Hide time axis

It is possible to hide time axis.

|

🎉 Copied!

|

|

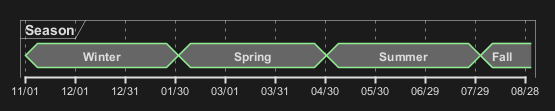

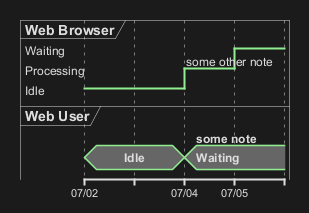

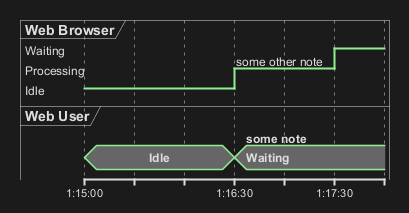

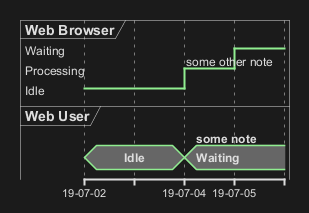

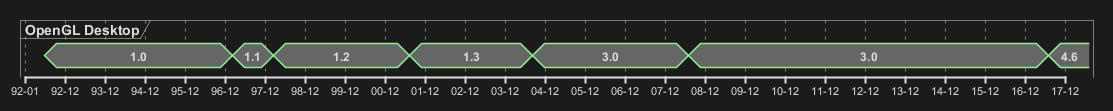

Using Time and Date

Using Time and Date

It is possible to use time or date.

|

🎉 Copied!

|

|

|

🎉 Copied!

|

|

[Ref. QA-7019]

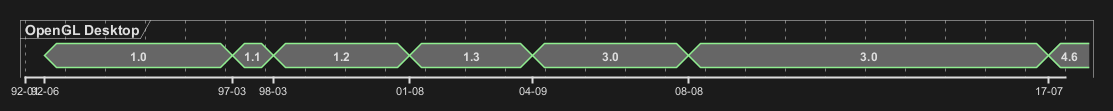

Change Date Format

Change Date Format

It is also possible to change date format.

|

🎉 Copied!

|

|

Manage time axis labels

Manage time axis labels

You can manage the time-axis labels.

Label on each tick (by default)

|

🎉 Copied!

|

|

Manual label (only when the state changes)

|

🎉 Copied!

|

|

[Ref. GH-1020]

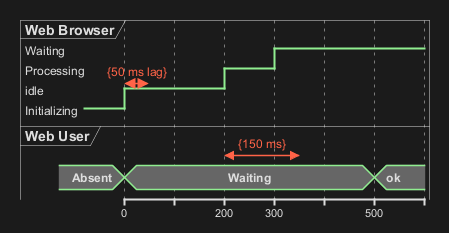

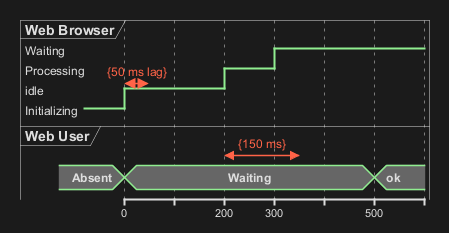

Adding constraint

Adding constraint

It is possible to display time constraints on the diagrams.

|

🎉 Copied!

|

|

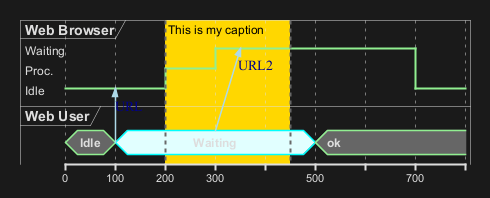

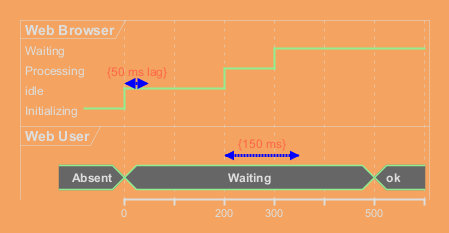

Zeitbereich hervorheben

Zeitbereich hervorheben

Im Diagramm kann mit ''highlight'' ein Zeitbereich definiert werden, der farblich hervorgehoben wird.

|

🎉 Copied!

|

|

[Ref. QA-10868]

WARNING

This translation need to be updated. WARNING

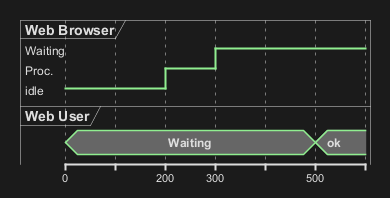

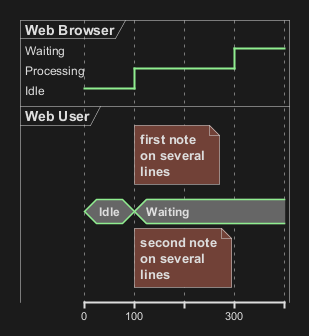

Using notes

Using notes

You can use the note top of and note bottom of

keywords to define notes related to a single object or participant (available only for concise or binary object).

|

🎉 Copied!

|

|

[Ref. QA-6877, GH-1465]

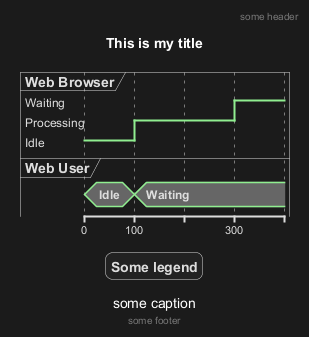

Adding texts

Adding texts

You can optionally add a title, a header, a footer, a legend and a caption:

|

🎉 Copied!

|

|

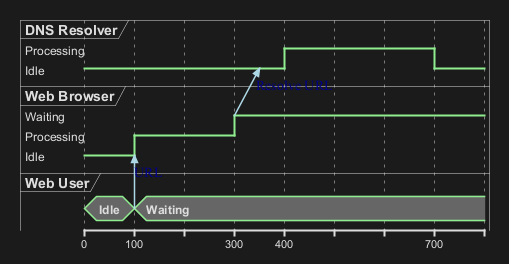

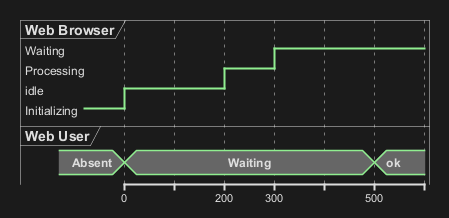

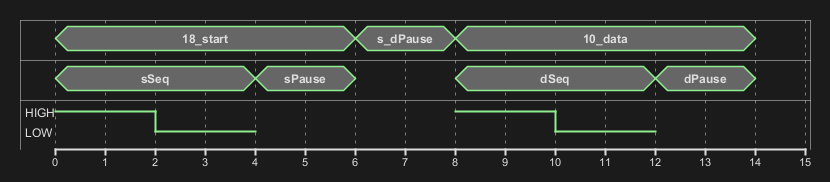

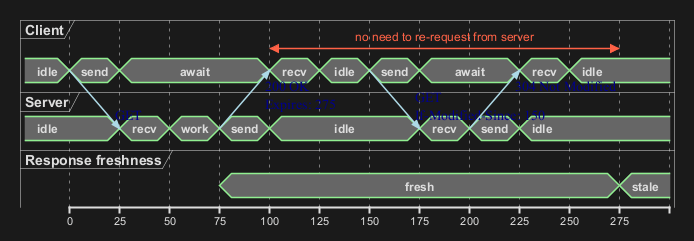

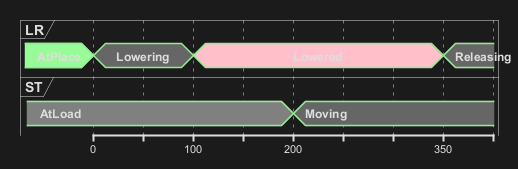

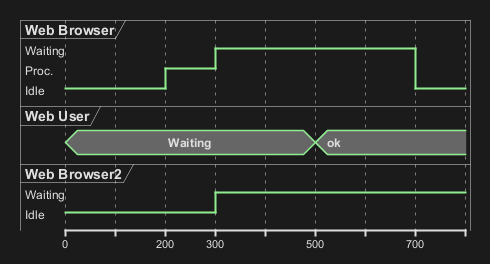

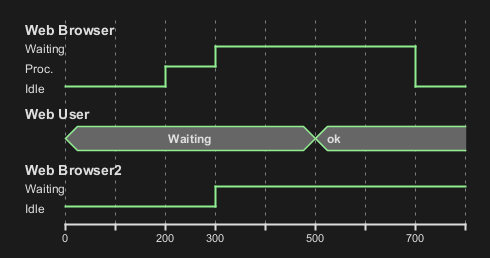

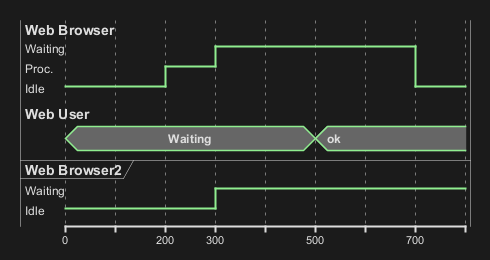

Complete example

Complete example

Thanks to Adam Rosien for this example.

|

🎉 Copied!

|

|

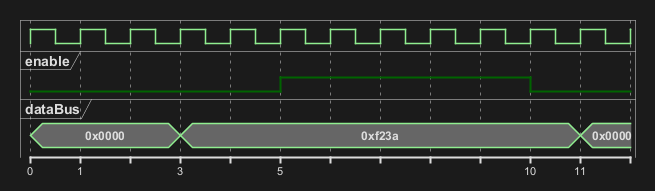

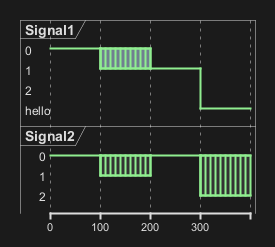

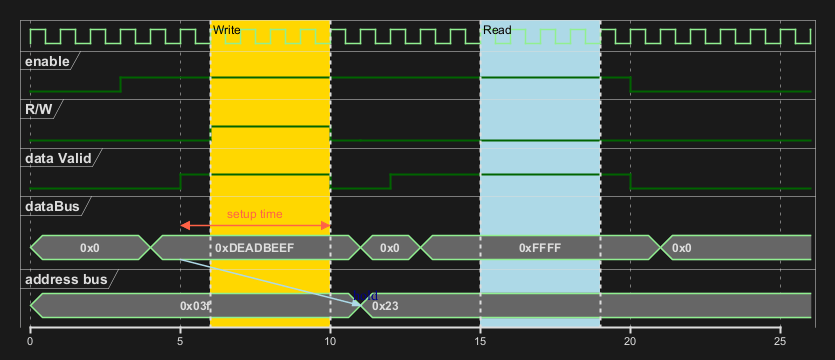

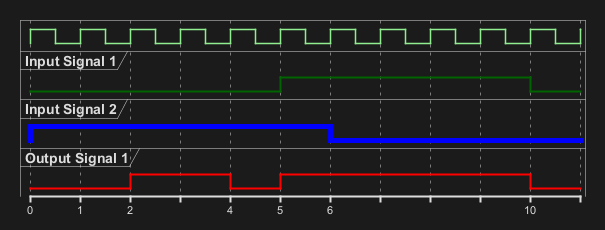

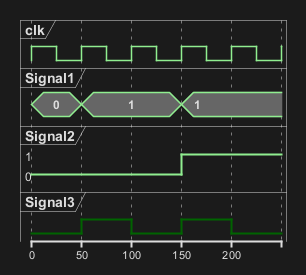

Digitales Beispiel

Digitales Beispiel

|

🎉 Copied!

|

|

Adding color

Adding color

You can add color.

|

🎉 Copied!

|

|

[Ref. QA-5776]

Using (global) style

Using (global) style

Without style (by default)

|

🎉 Copied!

|

|

With style

You can use style to change rendering of elements.

|

🎉 Copied!

|

|

[Ref. QA-14340]

Applying Colors to specific lines

Applying Colors to specific lines

You can use the <style> tags and sterotyping to give a name to line attributes.

|

🎉 Copied!

|

|

[Ref. QA-15870]

Compact mode

Compact mode

You can use compact command to compact the timing layout.

By default

|

🎉 Copied!

|

|

Global mode with mode compact

|

🎉 Copied!

|

|

Local mode with only compact on element

|

🎉 Copied!

|

|

[Ref. QA-11130]

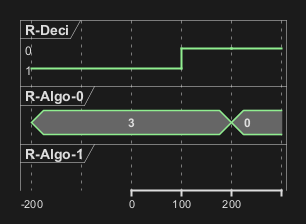

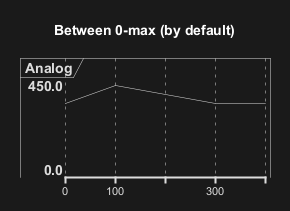

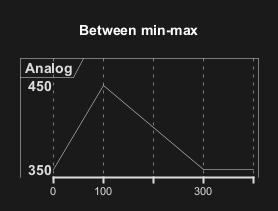

Scaling analog signal

Scaling analog signal

You can scale analog signal.

Without scaling: 0-max (by default)

|

🎉 Copied!

|

|

With scaling: min-max

|

🎉 Copied!

|

|

[Ref. QA-17161]

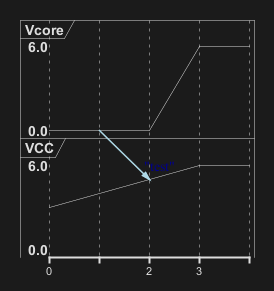

Customise analog signal

Customise analog signal

Without any customisation (by default)

|

🎉 Copied!

|

|

With customisation (on scale, ticks and height)

|

🎉 Copied!

|

|

[Ref. QA-11288]

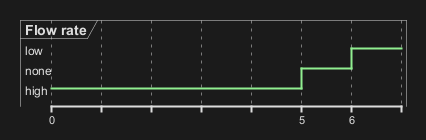

Order state of robust signal

Order state of robust signal

Without order (by default)

|

🎉 Copied!

|

|

With order

|

🎉 Copied!

|

|

With order and label

|

🎉 Copied!

|

|

[Ref. QA-6651]

Defining a timing diagram

Defining a timing diagram

By Clock (@clk)

|

🎉 Copied!

|

|

By Signal (@S)

|

🎉 Copied!

|

|

By Time (@time)

|

🎉 Copied!

|

|

[Ref. QA-9053]

Annotate signal with comment

Annotate signal with comment

|

🎉 Copied!

|

|

[Ref. QA-15762, and QH-888]