时序图

UML 中的时序图是一种特定类型的交互图,可视化系统的时序约束。它侧重于事件的时间顺序,展示不同对象如何随着时间的推移相互影响。定时图在实时系统和嵌入式系统中特别有用,可用于了解对象在整个给定时间段内的行为。 [Ref. of initial request QA-5383] 声明参与者

声明参与者

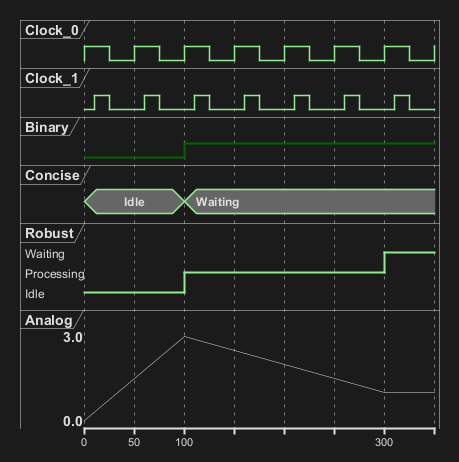

使用以下关键字声明参与者, 可根据需要选择显示样式。

| 关键词 | 描述 |

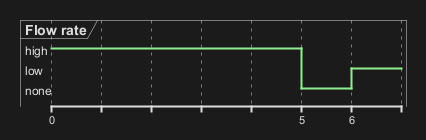

analog

|

模拟信号的变化是连续的,其值在给定值之间会进行线性插值。 |

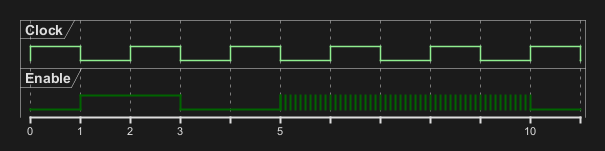

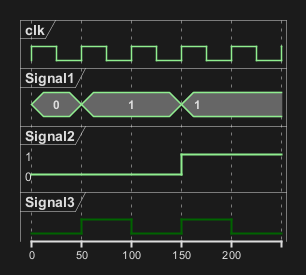

binary

|

二进制信号,只有两个状态。 (binary)

|

clock

|

时钟信号 ,即从高电平到低电平反复转换的信号,需要用period设置周期。可选的参数还有脉冲时长pulse和偏移量offset

|

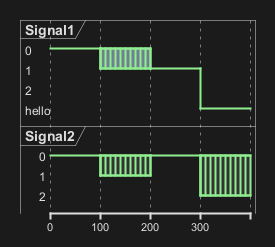

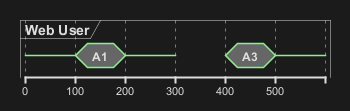

concise

|

简明的图形化数据表示,可表示数据的移动(非常适合表示信息)。 |

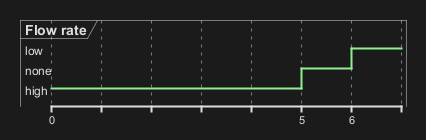

robust

|

用信号线表示的状态,便于呈现状态间的转化(可设置多种状态)。 |

@ 标注, 和 is 动词定义状态.

WARNING

This translation need to be updated. WARNING

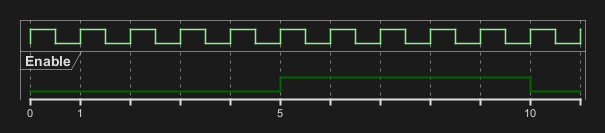

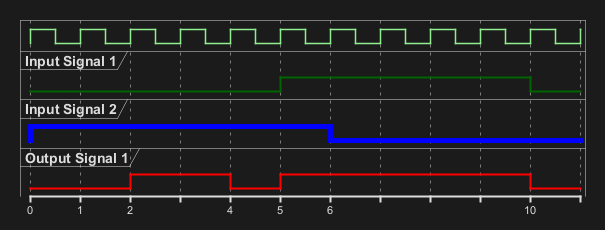

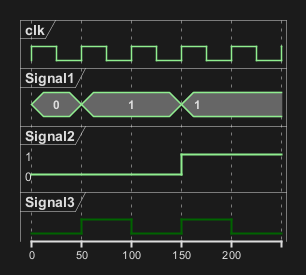

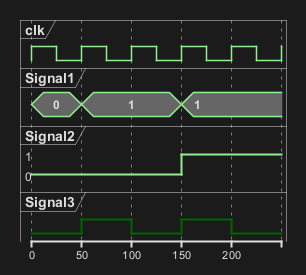

二进制及时钟信号

二进制及时钟信号

使用以下关键字可以绘制二进制及时钟信号:

binaryclock

增加标示

增加标示

使用下述的语法,增加对某一时刻信号变动的描述。

WARNING

This translation need to be updated. WARNING

相对时间

相对时间

可以使用 @+和@- 符号表示相对时间.

锚点

锚点

,而不是在绝对时间上使用绝对时间或相对时间,你可以通过使用as 关键字和以: 开始的名称来定义一个时间作为锚点。

@XX as :<anchor point name>

Anchor Points with decimal offset

Anchor Points with decimal offset

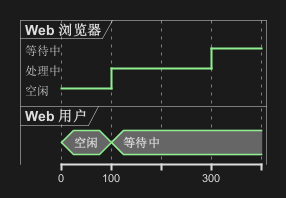

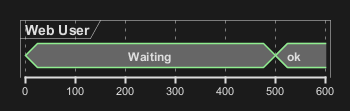

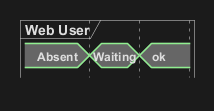

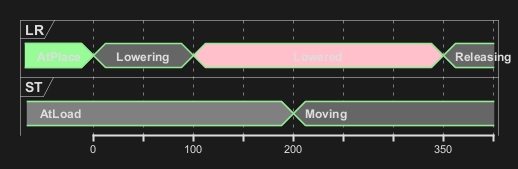

参与者

参与者

按时间顺序来描述状态变化可能会有些麻烦,不如将每个参与者的变化放在一起。

设置缩放

设置缩放

你还可以设置缩放比例。

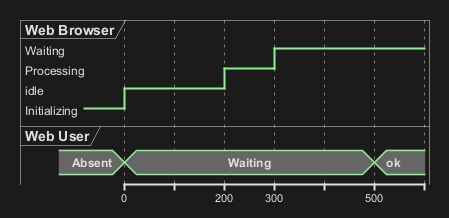

初始状态

初始状态

你可以定义初始状态。

模糊状态

模糊状态

一个信号在某个时段可能是模糊的,有多个可能的状态区间。

模糊或者未定义鲁棒状态信号

模糊或者未定义二进制信号

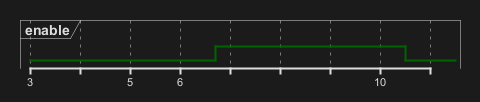

隐藏状态

隐藏状态

可以隐藏某个时段的状态。

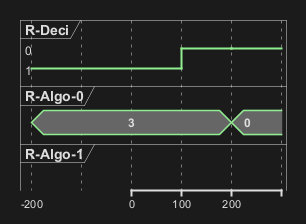

Negative time value

Negative time value

隐藏时间轴

隐藏时间轴

可以隐藏时间轴。

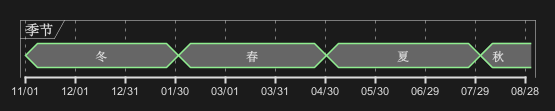

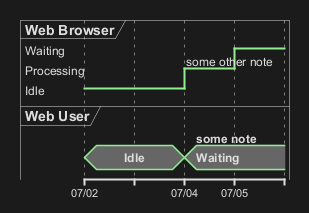

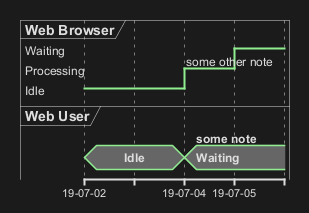

使用日期

使用日期

时间轴除时间以外也可以改用日期表示。

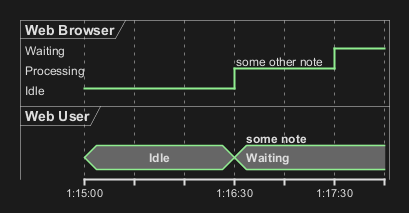

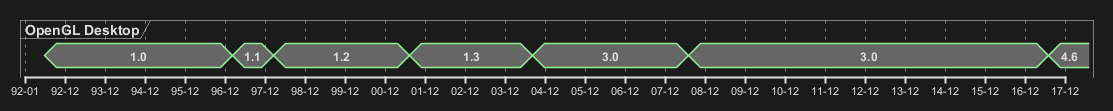

Change Date Format

Change Date Format

It is also possible to change date format.

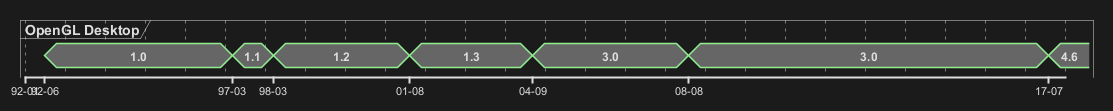

Manage time axis labels

Manage time axis labels

You can manage the time-axis labels.

Label on each tick (by default)

Manual label (only when the state changes)

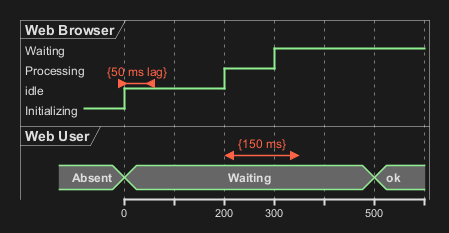

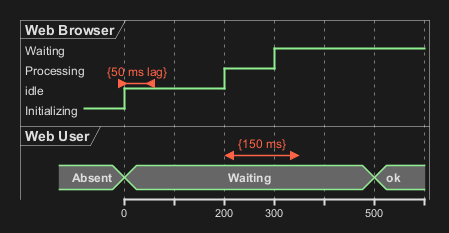

添加约束

添加约束

可以在图上标示时间约束。

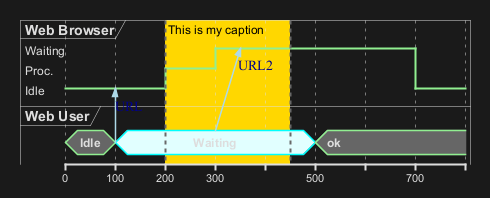

= 设置高亮

你可以给图表中的某一时段设置高亮。

WARNING

This translation need to be updated. WARNING

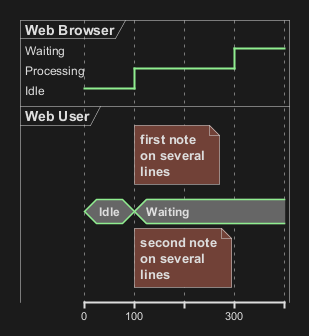

添加注释

添加注释

你可以使用 note top of 或 note bottom of 关键字在某一时刻或参与者的上方或下方添加注释 (只可以在 concise 类型的参与者中使用)。

WARNING

This translation need to be updated. WARNING

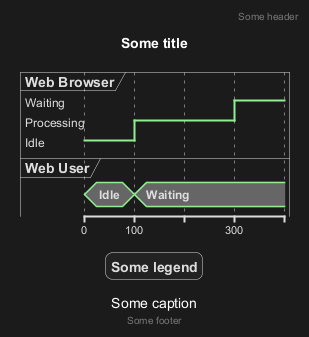

添加文本

添加文本

你可以选择添加标题、页眉、页脚、图例和说明。

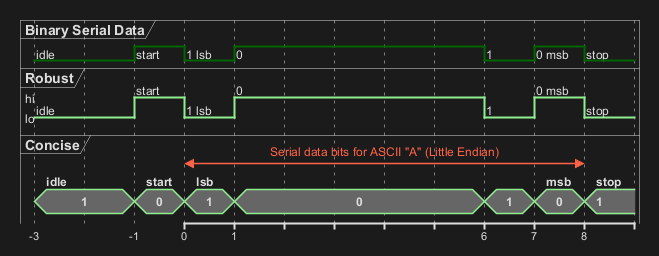

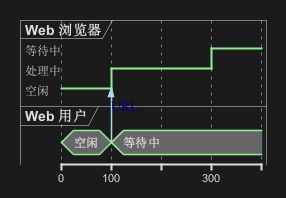

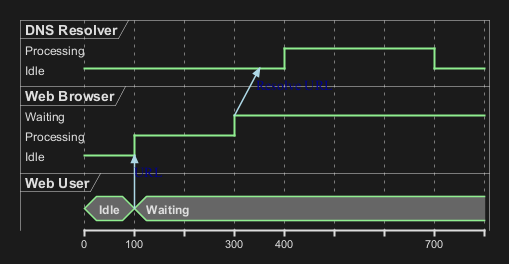

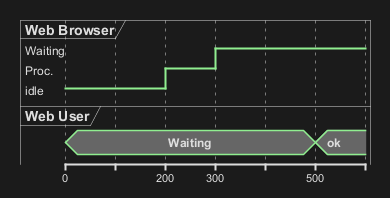

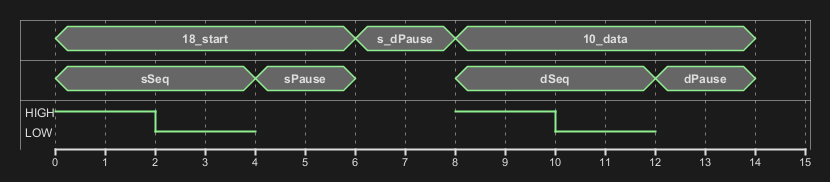

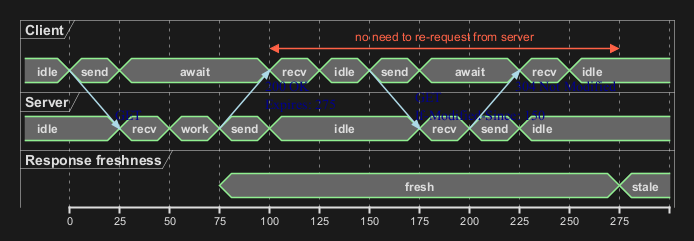

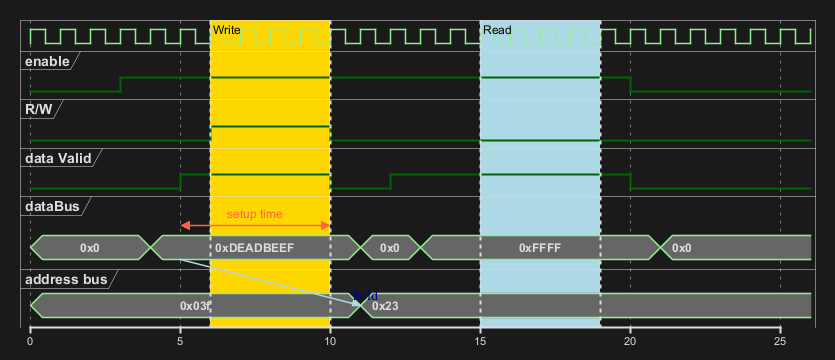

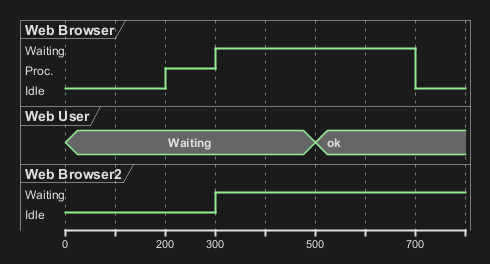

完整样例

完整样例

感谢Adam Rosien提供该样例。

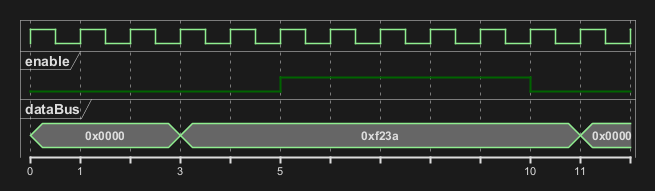

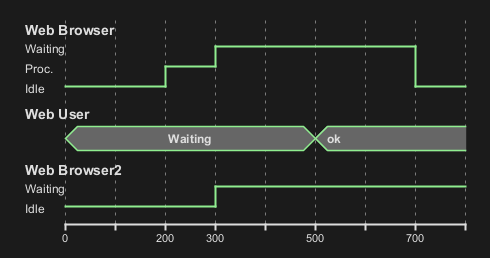

数据表示样例

数据表示样例

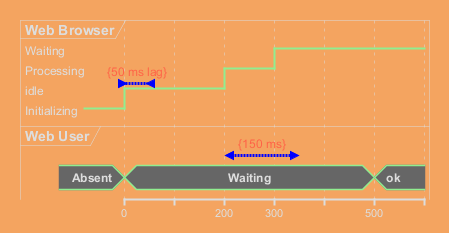

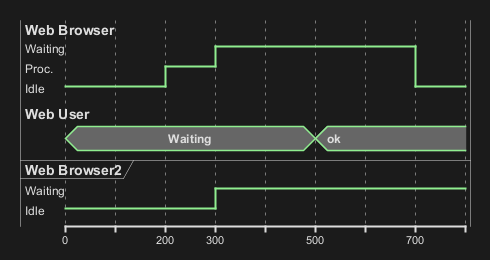

颜色

颜色

你可以为图表添加颜色。

使用(全局)样式

使用(全局)样式

无样式(默认样式)。

设置样式

你可以使用样式来改变元素的渲染。

对特定行着色

对特定行着色

可以使用 <style> 标记和模板将行属性命名

紧凑模式

紧凑模式

可以使用 compact 命令进行紧凑排版

默认模式

使用 mode compact 的全局紧凑模式

使用 compact 实现仅针对元素的局部紧凑模式

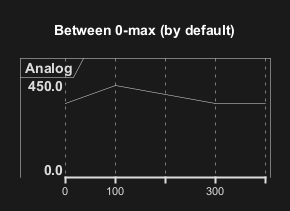

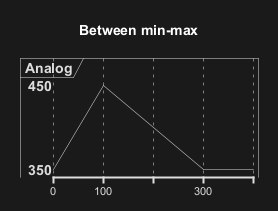

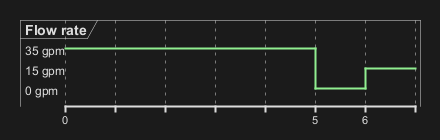

Scaling analog signal

Scaling analog signal

You can scale analog signal.

Without scaling: 0-max (by default)

With scaling: min-max

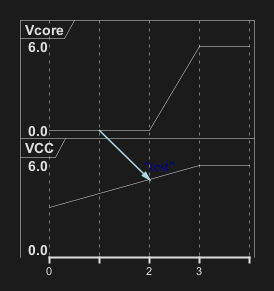

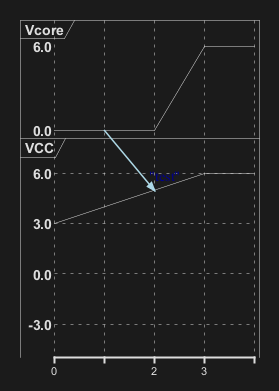

Customise analog signal

Customise analog signal

Without any customisation (by default)

With customisation (on scale, ticks and height)

Order state of robust signal

Order state of robust signal

Without order (by default)

With order

With order and label

Defining a timing diagram

Defining a timing diagram

By Clock (@clk)

By Signal (@S)

By Time (@time)

Annotate signal with comment

Annotate signal with comment